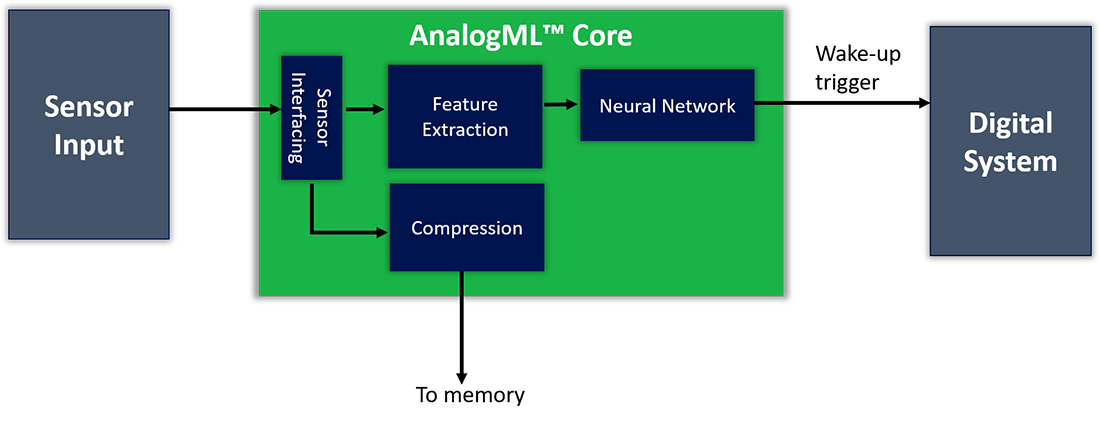

Aspinity AnalogML Core with Neuromorphic Computing Architecture for Low-power edge processing

Aspinity‘s analogML core features the improved capabilities of a tinyML chip with low-power analog neuromorphic computing architecture– with a system-level approach to low-power edge processing. Without making use of power-hungry digitization and digital processors, the analogML core is a fully analog inferencing solution built on the RAMP technology platform that classifies raw, unstructured sensor data in the domain of analog systems.

The elimination of extraneous data at the very beginning of the signal chain enhances the battery life of the analogML core by 10x or more. This feature is attributed to the implementation of always-on edge applications like voice activity detection, acoustic event detection, and vibration monitoring.

In the classic always-on edge system, data relevance can only be established after digitization as the ADC and digital processors consume the majority of system power. A digitize-first architecture is inefficient and wastes significant resources in evaluating data that will be discarded. On the other hand, in an analyze-first design, the analogML core reduces this inefficiency by introducing near-zero-power inferencing into the analog domain. Data relevance is evaluated prior to digitalization, allowing higher-power digital systems to remain off unless important data is identified.

“We’ve long realized that reducing the power of each individual chip within an always-on system provides only incremental improvements to battery life,” said Tom Doyle, founder and CEO, Aspinity. “That’s not good enough for manufacturers who need revolutionary power improvements. The AML100 reduces always-on system power to under 100µA, and that unlocks the potential of thousands of new kinds of applications running on battery.”

Made up of a number of software-controlled analog processing blocks, the analogML core can be activated, altered, and customized for a variety of analyze-first applications, including smart home, IoT, consumer, industrial, and biological applications. Since it is a purely analog-based processing device, each of the processing blocks can be powered individually as needed, hence there is no clock on the analogML core. The functionalities offered by the analogML core include interfacing of sensors, analog feature extraction, analog neural network, analog data compression.

Engineers can construct, assemble, and install application-specific analog machine learning models onto the analogML core using Aspinity’s efficient development environment. The analogML core was created for engineers without analog experience in mind, this allows the engineers to use conventional training data and programming interfaces that they are currently familiar with.

For more details on Aspinity’s AnalogML core, head to the product page.