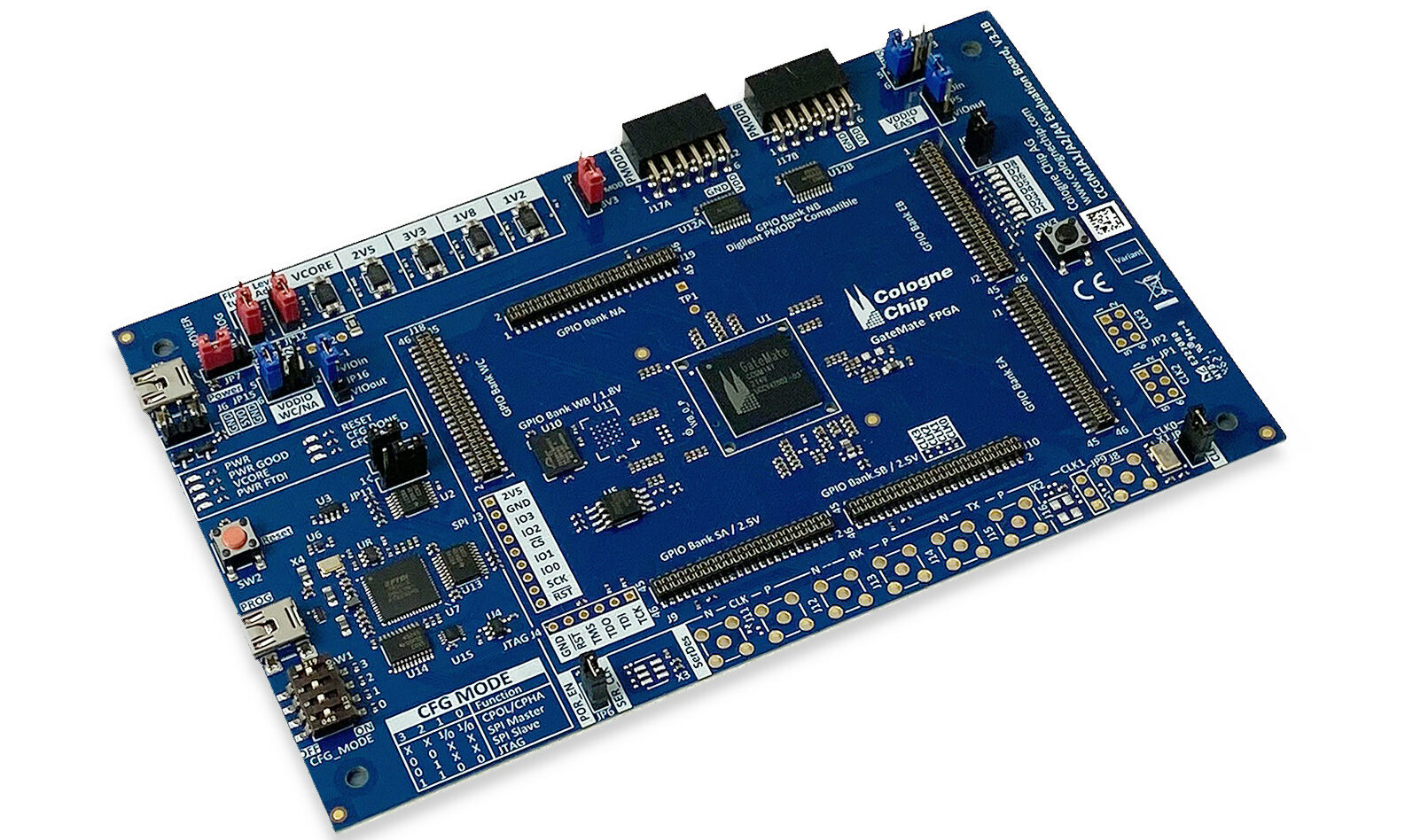

Cologne Chip has launched a new tool called the Integrated Logic Analyzer (ILA). It’s a free, open-source program designed for their GateMate A1 FPGA to help track internal signals. Unlike many FPGA companies that use completely proprietary tools, Cologne Chip combines a free, open-source framework with their tool. This ILA tool is aimed at making it easier for customers to find and fix problems in their FPGA designs.

The ILA allows you to find and fix issues in your GateMate FPGA design while it’s working. You can see all the design signals as waveforms on the FPGA itself. It’s like watching the data flow and correcting mistakes without interrupting your system’s usual operation.

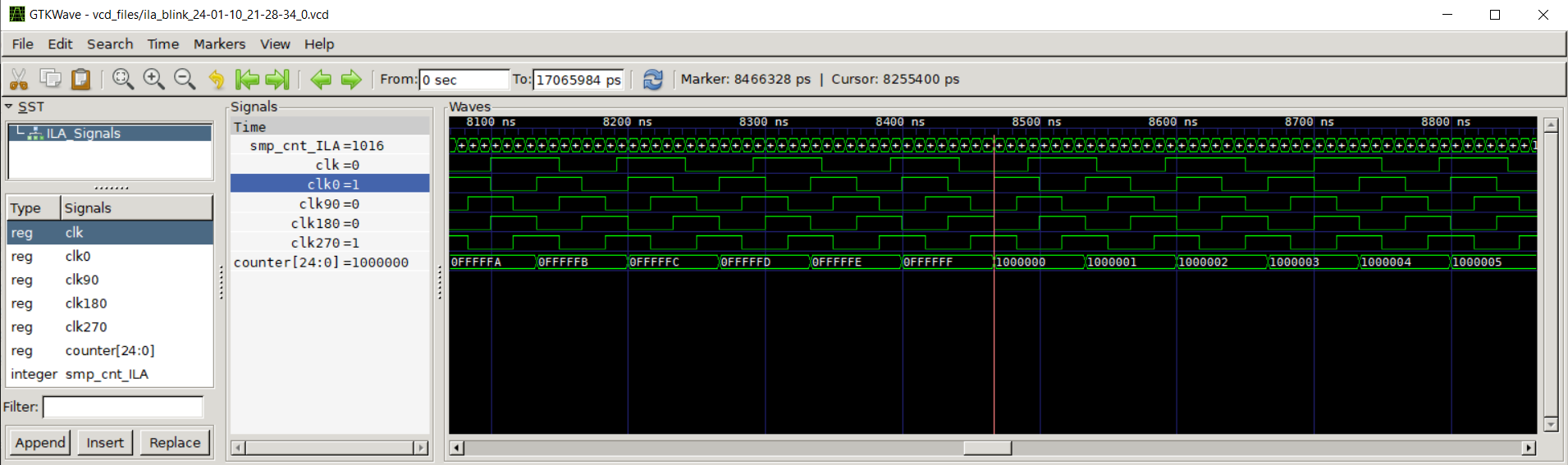

This project has two main parts: a Verilog-based digital circuit for the ILA and a Python program (ILA Control Program) for configuring the ILA during debugging. To use it, you’ll also need the GateMate FPGA toolchain and the open-source GTKWave program to see the captured waveforms. You can apply it to your own FPGA design or use one of the sample projects like “Blink,” which controls an LED based on a clock.

Key Benefits of ILA Tool for GateMate FPGA Debugging:

- Analyze 1000+ bits from all DUT signals simultaneously.

- User-friendly, interactive configuration shell.

- View design signals as waveforms within the FPGA with original names and sizes.

- Create custom trigger patterns using ‘1’ for high, ‘0’ for low, or ‘DC’ for flexibility.

- Maximize RAM for extended capture time.

- Define pre and post-trigger durations to focus on specific signal moments.

- Control DUT reset state in real-time for capture initiation.

- Easily set up multiple sequential captures with trigger adjustments.

- Detect rising or falling edges on desired signals.

- Reconfigure ILA via JSON files generated by the ILAcop program.

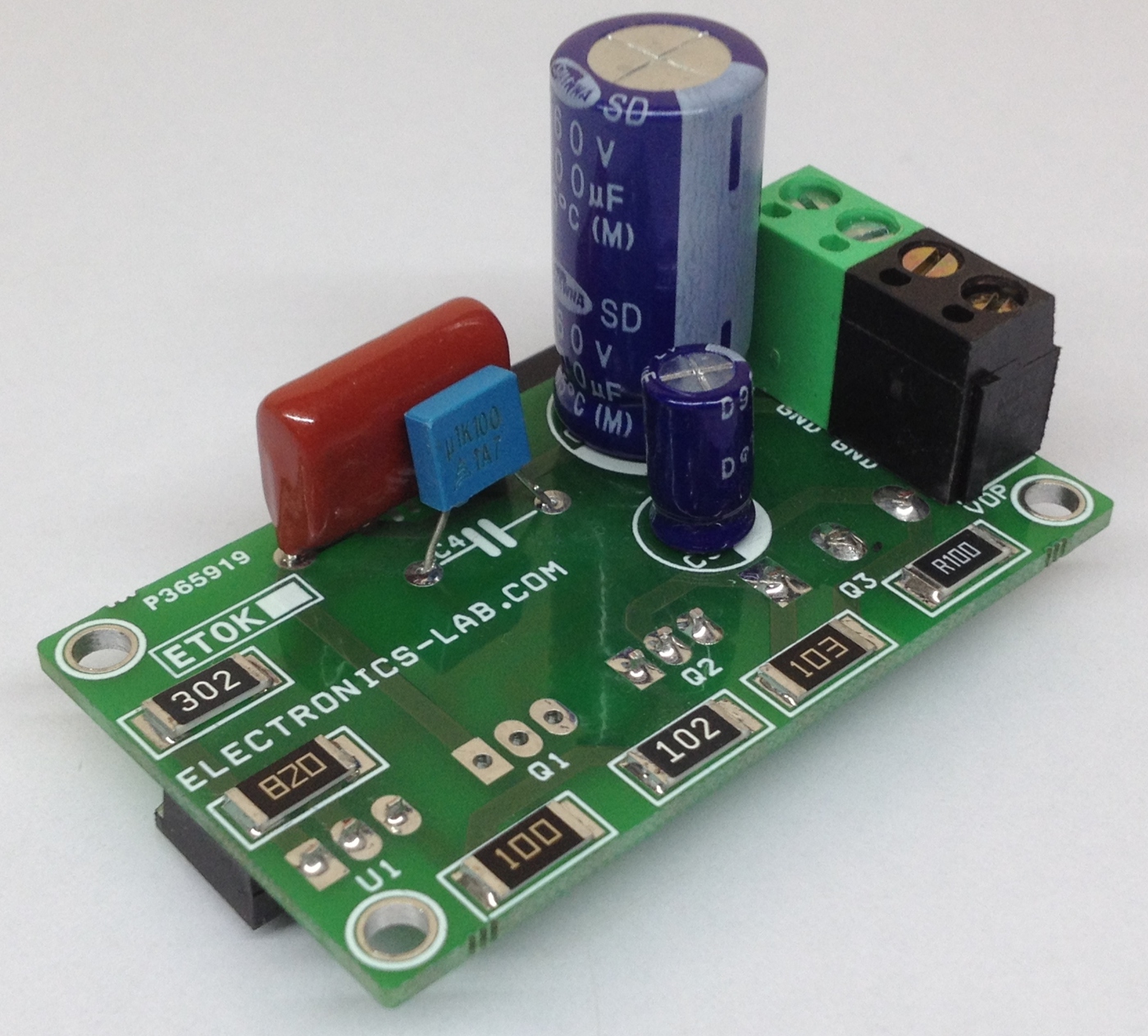

The project has been tested on the GateMate A1 FPGA board but should work with custom GateMate FPGA boards if they meet certain requirements. You can access the Verilog code, sample projects, Python program, and detailed documentation on the GitHub project page.