Developed in the dark hours of the night, between 2 and 8 o’clock in the morning of August 19th by Marcelo Samsoniuk, the DarkRISC-V stack is an experimental open source implementation of the RISC-V standard targeting the low-cost Xilinx Spartan-6 family of FPGAs. Following a week of debugging, Samsoniuk has released the implementation to GitHub under a BSD license.

Marcelo Samsoniuk’s says:

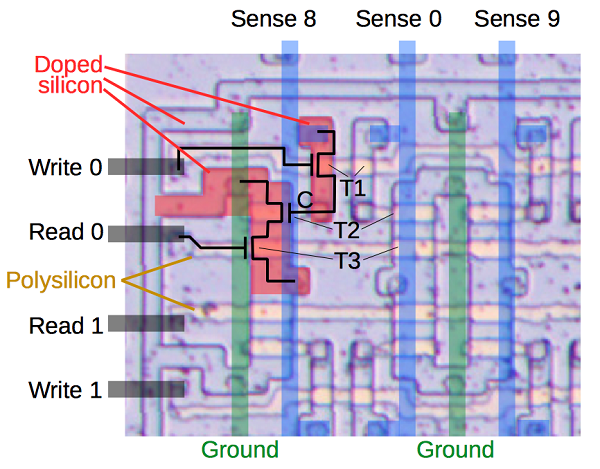

The general concept is based in my other early RISC processors and composed by a simplified two stage pipeline where a instruction is fetch from a instruction memory in the first clock and then decoded/executed in the second clock. The pipeline is overlapped without interlocks, in a way the DarkRISC-V can reach the performance of one clock per instruction most of time (the exception is after a branch, where the pipeline is flushed and one clock is lost). As addition, the code is very compact, with around two hundred lines of obfuscated but beautiful Verilog code.

Although the code is small and crude when compared with other RISC-V implementations, the DarkRISC-V has lots of impressive features:

- Implements most of the RISC-V RV32I instruction set.

- Works up to 75MHz and sustain 1 clock per instruction most of the time

- Flexible Harvard architecture (easy to integrate a cache controller)

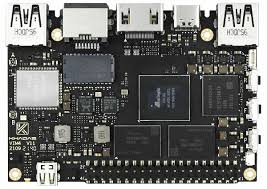

- Works fine in a real spartan-6 lx9

- Works fine with gcc 9.0.0 for RISC-V (no patches required!)

- Uses only around 1000 LUTs (spartan-6, core only)

- It has BSD license.

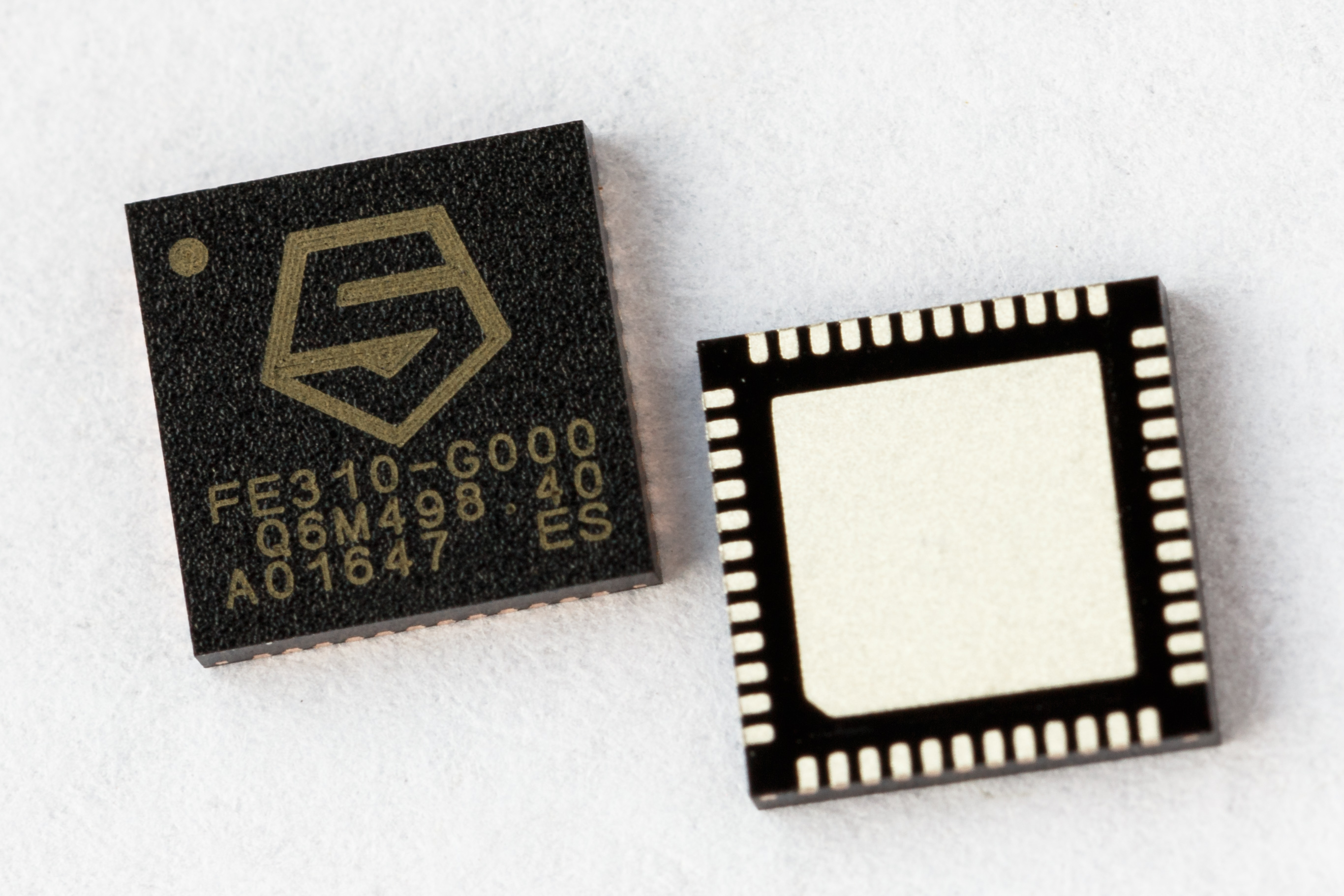

With the first GAP8 processor samples by Open-Silicon shipping, we’re almost approaching a period where we have multiple vendors producing open silicon built around the RISC-V core, and when that happens we’ll be in a very different place. At that point, we’re in a real open hardware environment because we no longer have vendor lock in, and it’s going to be interesting to see whether that makes a difference to the availability of boards based on RISC-V.

Until then, however, the availability of implementations of the RISC-V architecture, and the ability for people to get hands on with it—whether that’s using an FPGA or not—is important to the ecosystems continued health.

For instructions on how to implement RISC-V visit its GitHub Repository.