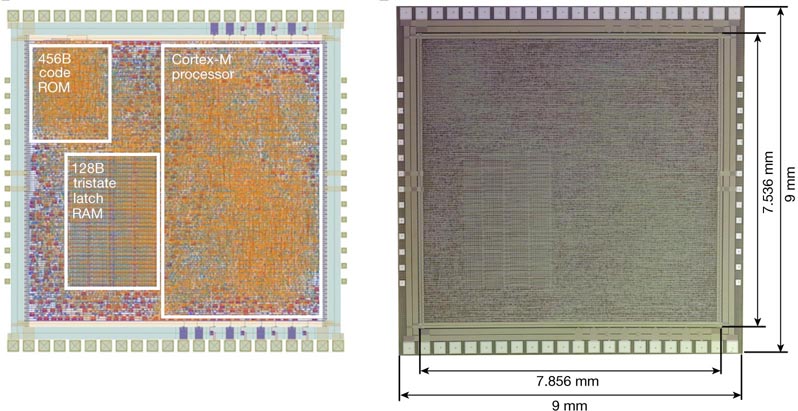

The microcontroller, detailed in the journal Nature after six years of development, includes a 32bit CPU, Nested Vector Interrupt Controller (NVIC) for handling interrupts from external devices, peripherals, memories and AHB-lite bus interface as well as a read only memory with 456 bytes that holds three test programs using the ARMv6-M instruction set and the standard ARM toolchain.

The whole system-on-chip runs at a clock rate of 29 kHz from a 3 V supply and consumes 21 mW, dominated by the static power, with the processor accounting for 45 percent, memories 33 percent and peripherals 22 percent.

The PlasticARM is 12 times larger than the previous development between ARM and PragmatIC on a dedicated machine learning core and marks a significant step for low cost flexible, plastic electronics for everyday objects to connect to the Internet of Things.

The SOC was implemented with PragmatIC’s 0.8-μm process using industry-standard chip implementation tools and four metal layers on a 200 mm polyimide wafer.

The resulting chip has an area of 59.2 mm2 (without pads), and contains 18,334 NAND-equivalent gates with 28 pins, which include clock, reset, GPIO, power and other debug pins. There are no dedicated electrostatic discharge mitigation techniques used in this design. Instead, all inputs contain 140 pF capacitors, whereas all outputs are driven by output drivers with active pull-up transistors.

A key challenge is the power consumption and heat dissipation in the plastic. ARM is developing lower-power cell libraries to support more complex plastic designs up to about 100,000 gates which will enable more peripherals around the controller core. Moving to more than 1,000,000 gates will probably require complementary metal–oxide–semiconductor (CMOS) technology, say the researchers.

Another challenge is to develop the programmable non-volatile memories for program storage.