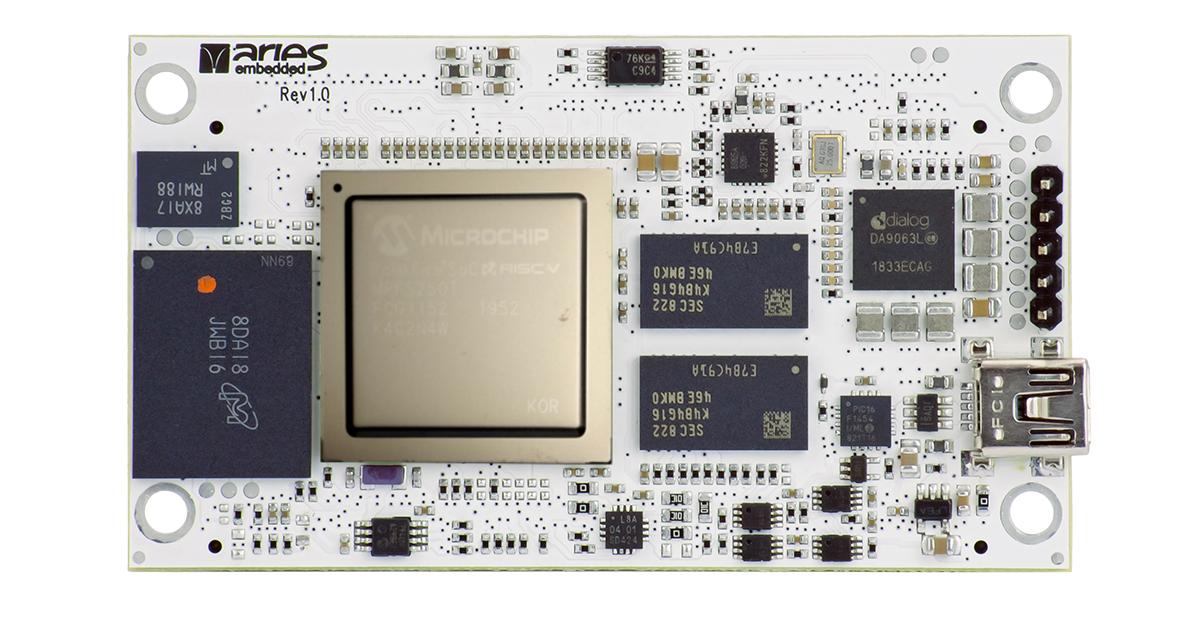

The M100PFS is based on the PolarFire SoC FPGA architecture by Microsemi and combines high-performance 64-bit RISC-V cores with outstanding FPGA technology. The platform integrates a hardened real-time, Linux capable, RISC-V-based MPU subsystem on the mid-range PolarFire FPGA family, bringing low power consumption, thermal efficiency and defence grade security to embedded systems.

The RISC-V CPU micro-architecture implementation is a simple 5 stage, single issue, in-order pipeline that doesn’t suffer from the Meltdown and Spectre exploits found in common out-of-order machines. All five CPU cores are coherent with the memory subsystem allowing a versatile mix of deterministic real time systems and Linux in a single multi-core CPU cluster.

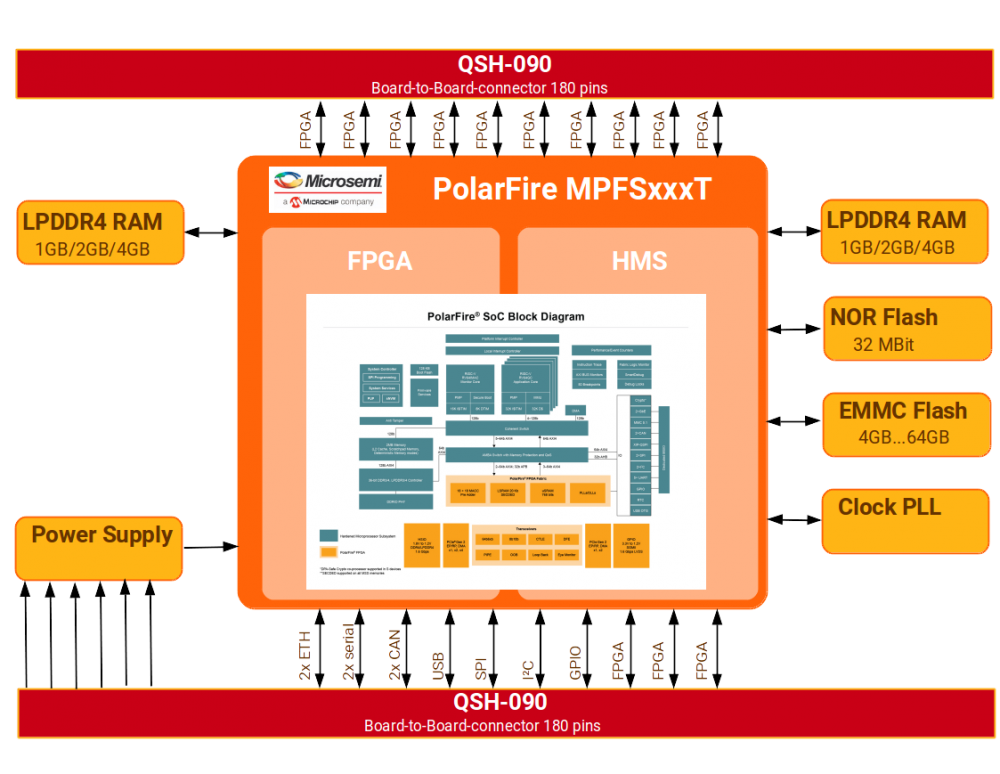

Block Diagram

Features:

- Microsemi PolarFire SoC FPGA

-

- MPFS025T

23KLE, 68 math blocks, 4x SERDES 12.5Gbit/s, 2x PCIe root port/end point - MPFS095T, available on request

93KLE, 292 math blocks, 4x SERDES 12.5Gbit/s, 2x PCIe root port/end point - MPFS160T, available on request

161KLE, 498 math blocks, 8x SERDES 12.5Gbit/s, 2x PCIe root port/end point - MPFS250T

254KLE, 784 math blocks, 16x SERDES 12.5Gbit/s, 2x PCIe root port/end point

- MPFS025T

-

- Quad 64-bit RV64GC cores, 667 MHz

- 64-bit RV64IMAC monitor core, 667 MHz

- Processor I/O

- 2x Gigabit Ethernet

- 1x USB 2.0 OTG

- 1x MMC 5.1 SD/SDIO

- 2x CAN 2.0 A and B

- Execute in place Quad SPI flash controller

- 5x multi-mode UARTs

- 2x SPI, 2 I2C

- RTC, GPIO

- 5x watchdog timers

- timers

- Processor to FPGA Interconnect

- 2 64-bit AXI4 processor-to-fabric interfaces

- 3 64-bit AXI4 fabric-to-processor interfaces

- 1 32-bit APB processor-to-fabric interface

- 1/2/4 GByte LPDDR4 RAM dedicated to the HMS

- 1/2/4 GByte LPDDR4 RAM dedicated to the FPGA

- 32 Mbit NOR Flash

- 4 – 64 GByte eMMC memory

- Clock distribution

- default configuration:

- Gigabit Ethernet

- UART

- CAN

- SPI

- I²C

- USB

- single 3,3V supply

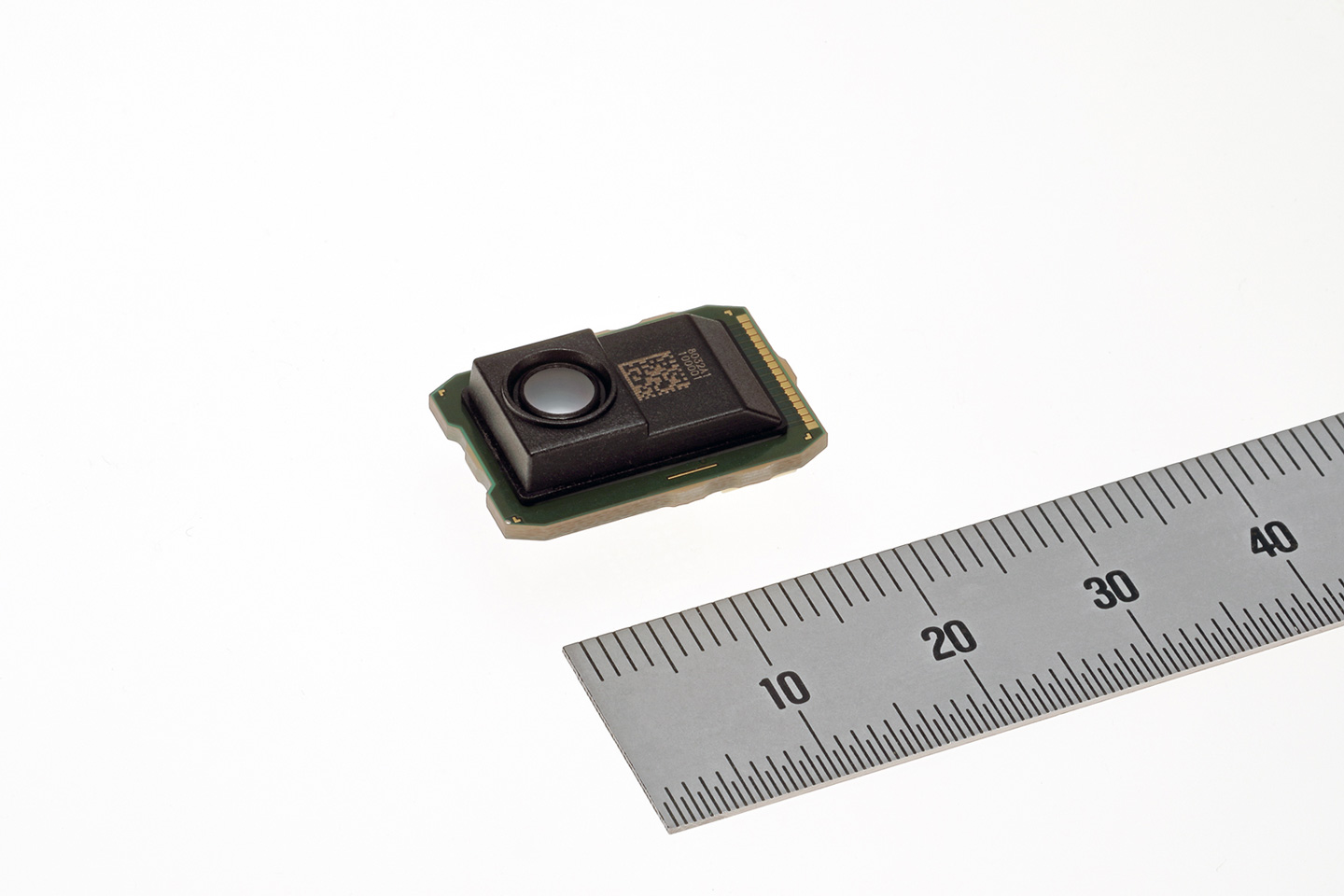

- size 74mmx42mm

- 2 x Samtec QSH-090-01-F-D-A board-to-board interconnect

Schedule & Availability

The M100PFS are currently under development, first boards are to be expected appr. in Q3/2020