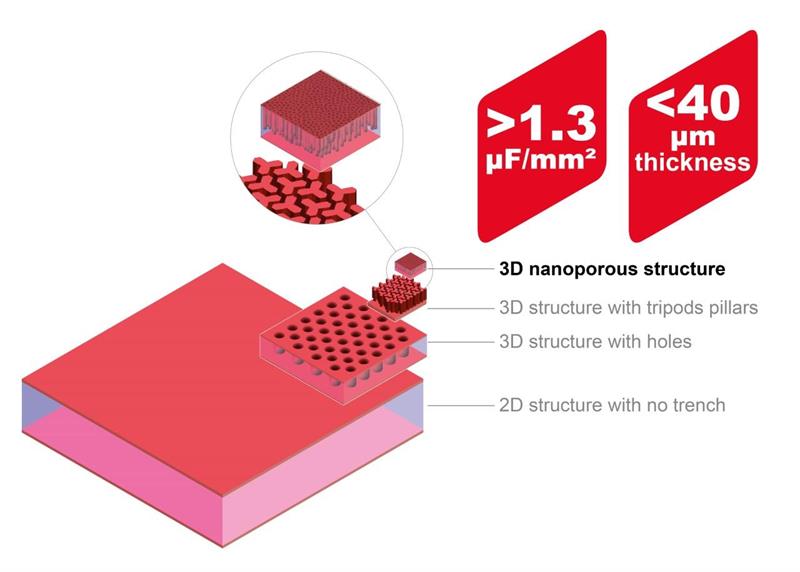

Murata has developed a silicon process technology capable of fabricating silicon capacitors with a density of 1.3 µF/mm².

Intended for the mobile and high-performance computing (HPC) markets these devices have an extremely low ESL (few pH) and low ESR (few mΩ) which support the high performance of new power distribution networks (PDN) that require low impedance over a wide frequency bandwidth.

As digital ICs evolve to offer more features at lower voltages, resolving issues like noise and voltage fluctuation is critical, so with its <40 µm profile chip designer engineers will be able to embed the silicon capacitor into the package as close to the active die as possible, minimizing the current’s effective path length and reducing parasitics.

These multi-terminal devices satisfy the various SoC and microprocessor design requirements for multiple terminal capacitor networks. Replacing conventional monolithic ceramic capacitors with multi-terminal silicon devices reduces the total quantity of capacitors required on the board significantly and will help to improve the overall compactness of the end design.

Fewer capacitors will also result in total savings in both bills of materials and mounting costs.

more information: http://www.murata.com