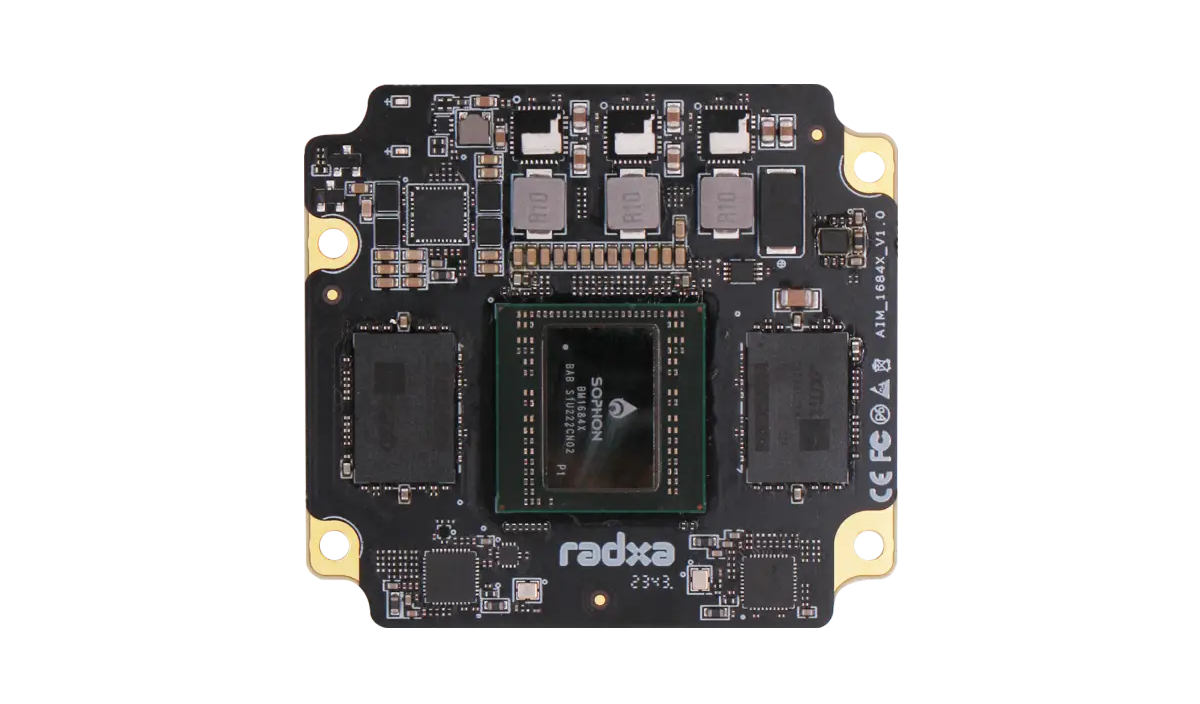

Radxa Unveils AICore SG2300x Module: Powering Edge AI with 32 TOPS Performance

Radxa’s AICore SG2300x Module Brings 32 TOPS to Bear on Edge AI, On-Device Generative AI

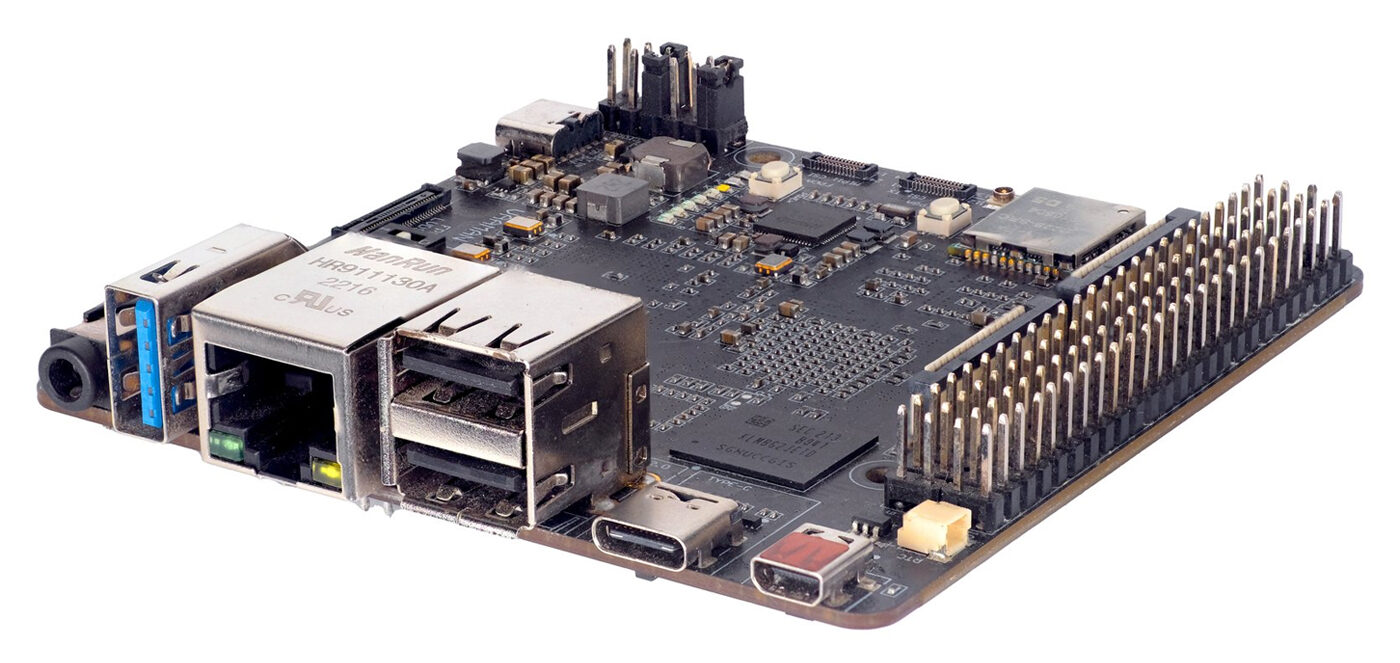

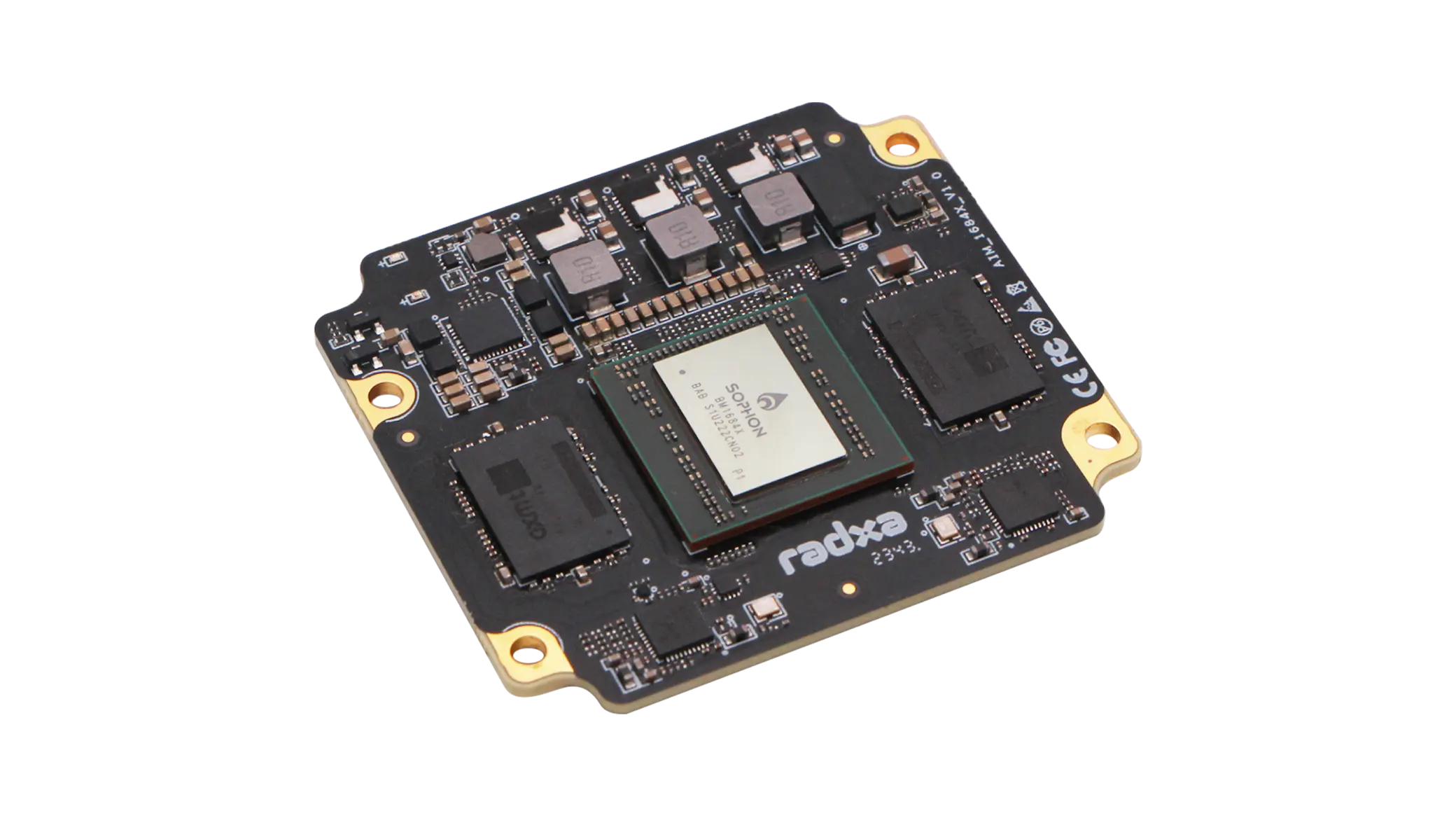

Radxa, a leading name in embedded computing, is set to revolutionize edge artificial intelligence (AI) with its latest offering: the AICore SG2300x system-on-module (SOM). Promising an impressive 32 tera-operations per second (TOPS) of compute performance, this module is poised to drive on-device AI to new heights.

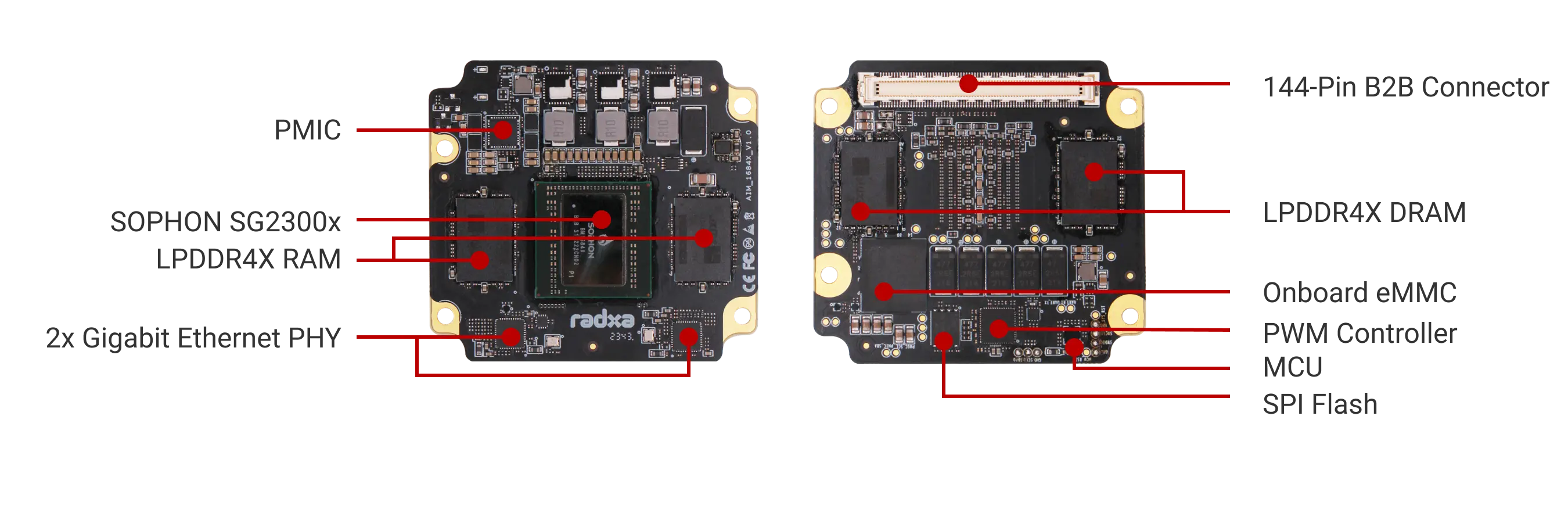

At the heart of the AICore SG2300x lies the SOPHON SG2300x system-on-chip, boasting eight Arm Cortex-A53 processor cores clocked at up to 2.3GHz. Augmenting this processing power is a dedicated tensor processing unit (TPU) coprocessor, delivering a claimed 32 TOPS at INT8 precision, with capabilities extending to 16 TOPS in FP16/BF16 precision and 2 TOPS at FP32 precision. Complementing this computational prowess is a generous 16GB of LPDDR4X RAM and a 64GB eMMC storage module, expandable via an SDMMC interface.

The AICore SG2300x is engineered to handle the demands of on-device AI, including large language models (LLMs) and generative AI models, with ease. Radxa highlights its compatibility with popular generative AI models such as generative pre-trained transformers (GPTs), the Stable Diffusion image generation model, and the ChatDOC model. For scenarios requiring even greater processing power, the module supports the “cascading” of two units to achieve up to 64 TOPS.

Radxa ensures seamless integration with leading machine-learning frameworks, including TensorFlow and PyTorch, through its BMNNSDK software development kit. The toolkit facilitates model optimization, and efficient runtime support, and provides access to a model zoo featuring pre-trained models like YoloV8, ResNet, PP-OCR, DeepSORT, and OpenPose.

In terms of connectivity, the module offers robust peripheral support, including one PCI Express 3.0 four-lane root complex and endpoint, up to three UART and three I2C buses, and 32 general-purpose input/output (GPIO) pins with two pulse-width modulation (PWM) channels. Additionally, it features dual gigabit Ethernet PHYs and hardware decoding for 32 channels of H.264/H.265 video at 1080p25, alongside encoding for 12 channels of H.264/H.265 at the same resolution and refresh rate.

While pricing and availability details are yet to be disclosed on the Radxa website, plans to release an open-source carrier board design and a design guide document for enthusiasts keen on building their systems.