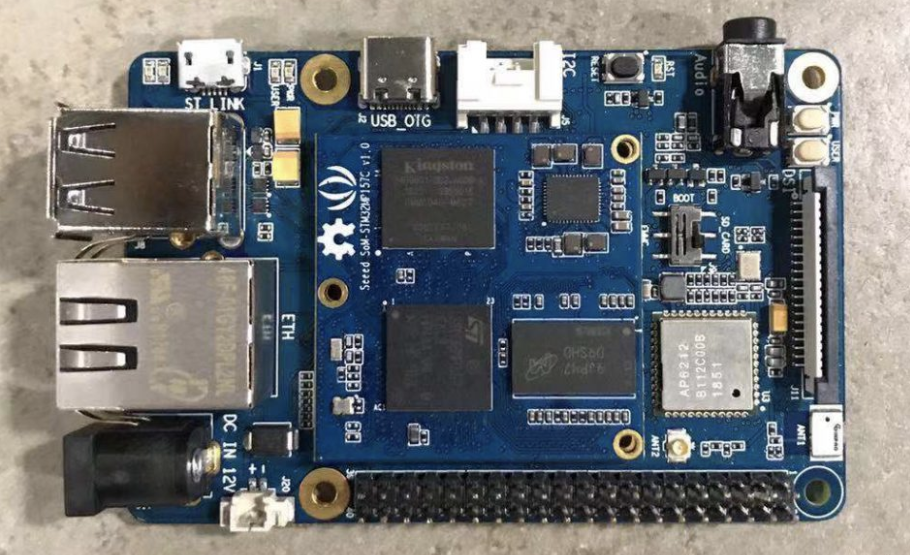

Odyssey-STM32MP157C joins τηε growing list of SBCσ developed by SeeedStudio. It comprises a baseboard device called the NPi-STM32MP157C and an SoM device based on an STMicroelectronics’ Arm Cortex A7/M4 hybrid SoC called the SOM-STM32MP157C.

SeeedStudio explains that it’s choice of the Cortex-A7 processor comes from it being a very energy efficient applications processor as it was designed to provide rich performance for high-end wearables, and other low-power embedded and consumer applications. It provides up to 20% more single-thread performance than the Cortex-A5 and provides similar performance to the Cortex-A9.

The device also embeds a Cortex -M4 32-bit RISC core operating at up to 209 MHz frequency. Cortex-M4 core features a floating-point unit (FPU) single precision which supports Arm single-precision data-processing instructions and data types. The Cortex-M4 supports a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

It provides an external SDRAM interface supporting external memories up to 8-Gbit density (1 Gbyte), 16 or 32-bit LPDDR2/LPDDR3 or DDR3/DDR3L up to 533 MHz.

The STM32MP157C also embeds a 3D graphics processing unit (Vivante – OpenGL ES 2.0) running at up to 533 MHz, with performances up to 26 Mtriangle/s, 133 Mpixel/s

The device offers two ADCs, two DACs, a low-power RTC, 12 general-purpose 16-bit timers, two PWM timers for motor control, five low-power timers, a true random number generator (RNG), and a cryptographic acceleration cell. The devices support six digital filters for external sigma-delta modulators (DFSDM) and also features standard and advanced communication interfaces

Some features include:

Core

- 32-bit dual-core Arm Cortex-A7

– L1 32-Kbyte I / 32-Kbyte D for each core

– 256-Kbyte unified level 2 cache

– Arm NEON™ and Arm TrustZone - 32-bit Arm Cortex-M4 with FPU/MPU with up to 209 MHz (Up to 703 CoreMark)

- Memory Features

– External DDR memory up to 1 Gbyte

– up to LPDDR2/LPDDR3-1066 16/32-bit

– up to DDR3/DDR3L-1066 16/32-bit

– 708 Kbytes of internal SRAM: 256 Kbytes of AXI SYSRAM + 384 Kbytes of AHB SRAM + 64 Kbytes of AHB SRAM in Backup domain and 4 Kbytes of SRAM in Backup domain

– Dual-mode Quad-SPI memory interface

– Flexible external memory controller with up to 16-bit data bus: parallel interface to connect external ICs and SLC NAND memories with up to 8-bit ECC - Secure boot, TrustZone peripherals, active tamper

- Cortex-M4 resources isolation

- Power Management Features

– 1.71 V to 3.6 V I/Os supply (5 V-tolerant I/Os)

– POR, PDR, PVD, and BOR

– On-chip LDOs (RETRAM, BKPSRAM, DSI 1.2 V, USB 1.8 V, 1.1 V)

– Backup regulator (~0.9 V)

– Internal temperature sensors

– Low-power modes: Sleep, Stop, and Standby

– LPDDR2/3 retention in Standby mode

– Controls for PMIC companion chip - Total current consumption down to 2 µA (Standby mode, no RTC, no LSE, no BKPSRAM, no RETRAM)

- Clock Management Features

– Internal oscillators: 64 MHz HSI oscillator, 4 MHz CSI oscillator, 32 kHz LSI oscillator

– External oscillators: 8-48 MHz HSE oscillator, 32.768 kHz LSE oscillator

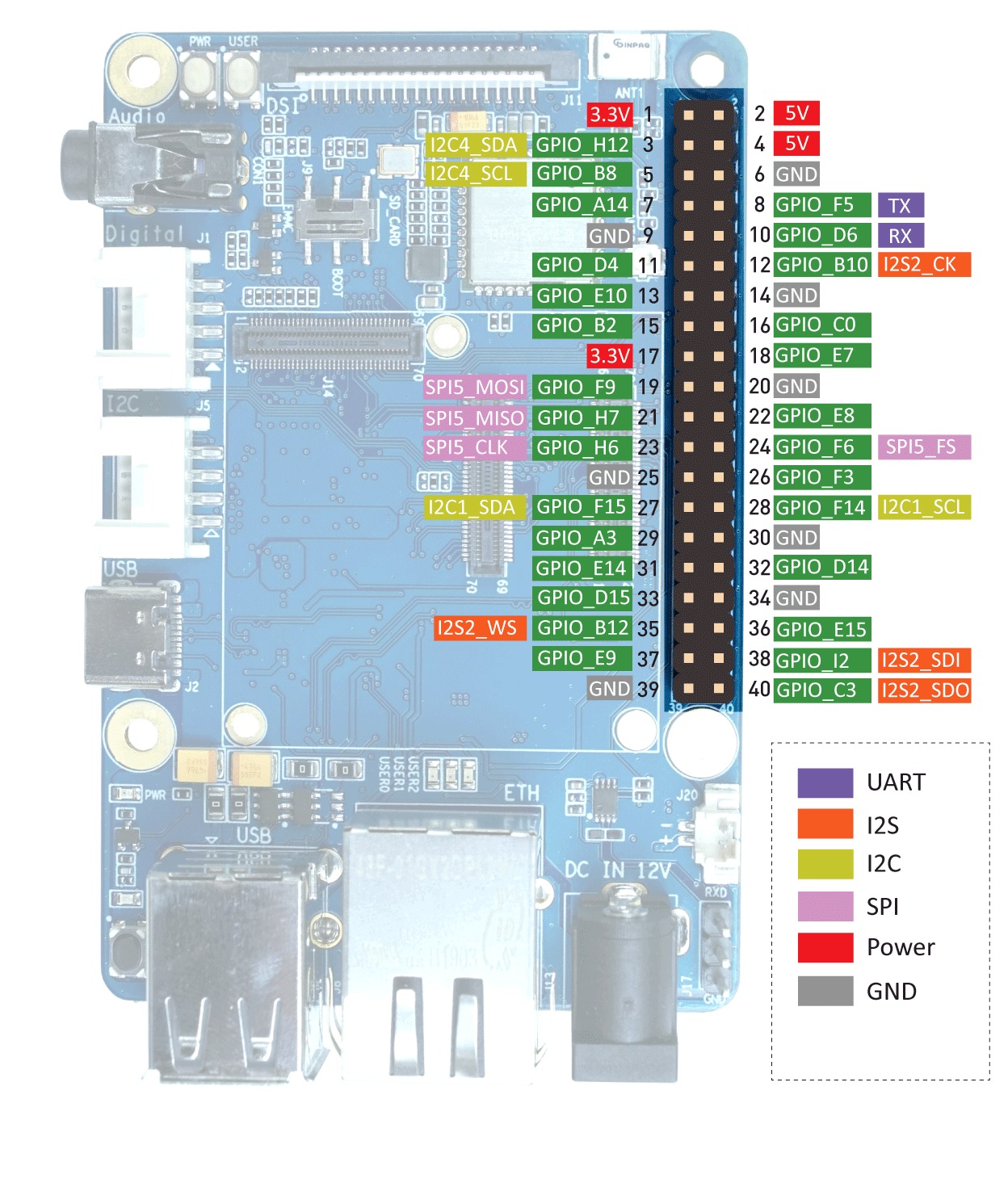

– 6 × PLLs with fractional mode - General-purpose input/outputs

– Up to 176 I/O ports with interrupt capability

– Up to 8 secure I/Os

– Up to 6 Wakeup, 3 tampers, 1 active tamper - 2 bus Interconnect matrices

– 64-bit Arm AMBA AXI interconnect, up to 266 MHz

– 32-bit Arm AMBA AHB interconnect, up to 209 MHz - 3 DMA controllers to unload the CPU

- 48 physical channels in total

- 1 × high-speed general-purpose master direct memory access controller (MDMA)

Odyssey is currently available for sale on Seeed Studio, Digi-Key and Mouser. More information on the board and its features can be found on Seeed’s Github page.