Tag: floating point

ETH Zurich Researchers Introduces A New RISC-V based Processor Architecture

For the growing demand for floating-point operations per second, a group of researchers at ETH Zurich (home for some significant RISC-V innovation) announced a new RISC-V-based processor architecture with substantial upgrades in performance and energy efficiency. The basic idea behind...

Continue Reading

RV32E Floating-Point library offers 72% code size reduction

SEGGER announces a new version of the RISC-V Floating-Point Library with full support for RV32E – the embedded variant of the RISC-V core. The new library leads to a massive reduction in code size for RISC-V applications using floating point. With all arithmetic functions hand-coded...

Continue Reading

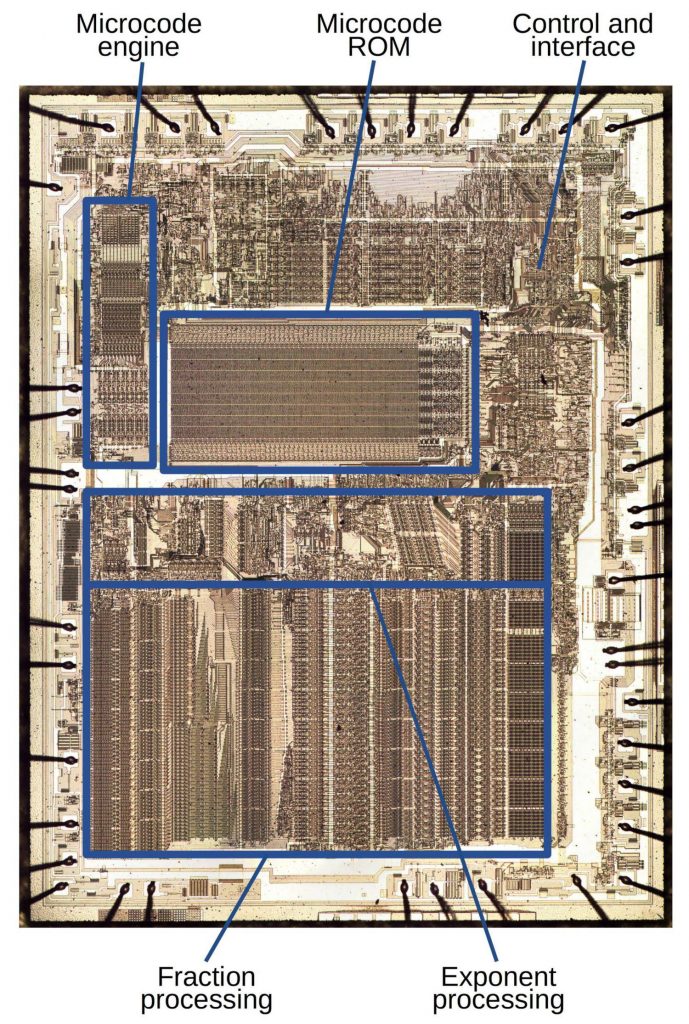

Two bits per transistor: high-density ROM in Intel’s 8087 floating point chip

Ken Shirriff has a detailed write-up about the multi-level ROM in Intel’s 8087 floating point chip: The 8087 chip provided fast floating point arithmetic for the original IBM PC and became part of the x86 architecture used today. One unusual feature of the 8087 is it contained a...

Continue Reading