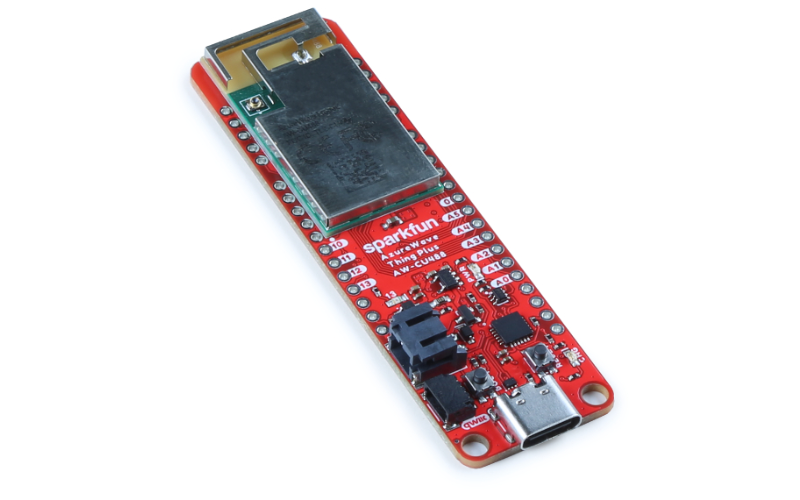

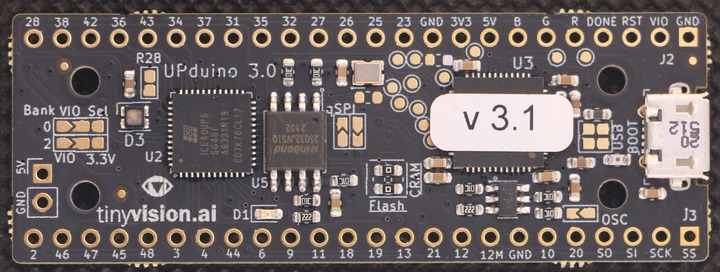

UPduino v3.1 is a compact and cost-efficient open-source FPGA board dedicated to applications that involve sensitive signal conditioning. It comprises of FTDI FPGA programmer, flash memory, a 3-color LED and FPGA pins for quick prototyping. The all-new UPduino v3.1 is an updated version of its predecessor where it improves on the shortcomings and limitations of its predecessors. The feedback from the discord community users is taken into consideration, and hence the changes to the board have been done accordingly.

The feedback from the users highlights the following:

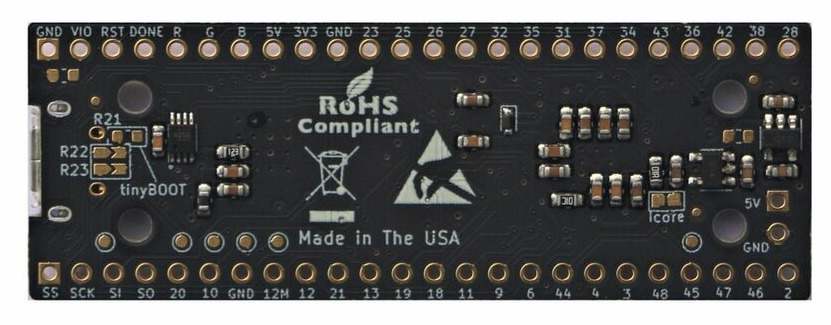

- To fix the 12MHz and Ground silkscreen bug

- The users were also facing an evident burning issue in the ferrite bead while shorting the 5v to the ground. So the users recommended replacing the USB filter ferrite bead with PTC in order to eliminate the burning issue. For more details visit the blog

To mark the changes made for issues mentioned above, the company has added a sticker denoting v3.1. The upgrades are visible in the APIO board files as well as the EEPROM to show v3.1, indicating the most recent version.

Features of UPduino v3.1:

- A Lattice UltraPlus ICE40UP5K edge intelligent FPGA strengths the UPduino v3.1 for low-power machine learning and AI connectivity. It features 8 multipliers, 1Mb SRAM and 120kb DRAM, making memory operations more efficient.

- It has 3.3v and 1.2v regulators, 5.3k LUTs (LookUp Tables) and FTDI FT232H USB. FTDI FT232H operates at 400Mbps and is a fast single-channel bridge chip that allows for flexible serial/parallel connectivity.

- UPdunio v3.1 comes with 39 GPIO (General Purpose Input/Output) pins to perform digital input/output functions. It requires 5V/3.3V/Ground to supply project DC power (<200mA).

- The oscillator running at 12MHz generates a clock by itself when the UPduino powers up. An optional jumper routes the generating clock to the FTDI, an external pin, and a global buffer on the FPGA board.

- The board’s PMOD (Peripheral Module Interface) compatibility makes it an ideal technique for enhancing its capabilities.

- Furthermore, it consists of 4MB QSPI (Quad Serial Peripheral Interface) Flash memory essentially providing 8x the bandwidth on the SPI bus. In reality, this bandwidth boost will only occur for burst read/writes. It also includes an RGB LED indicating the operation of the board.

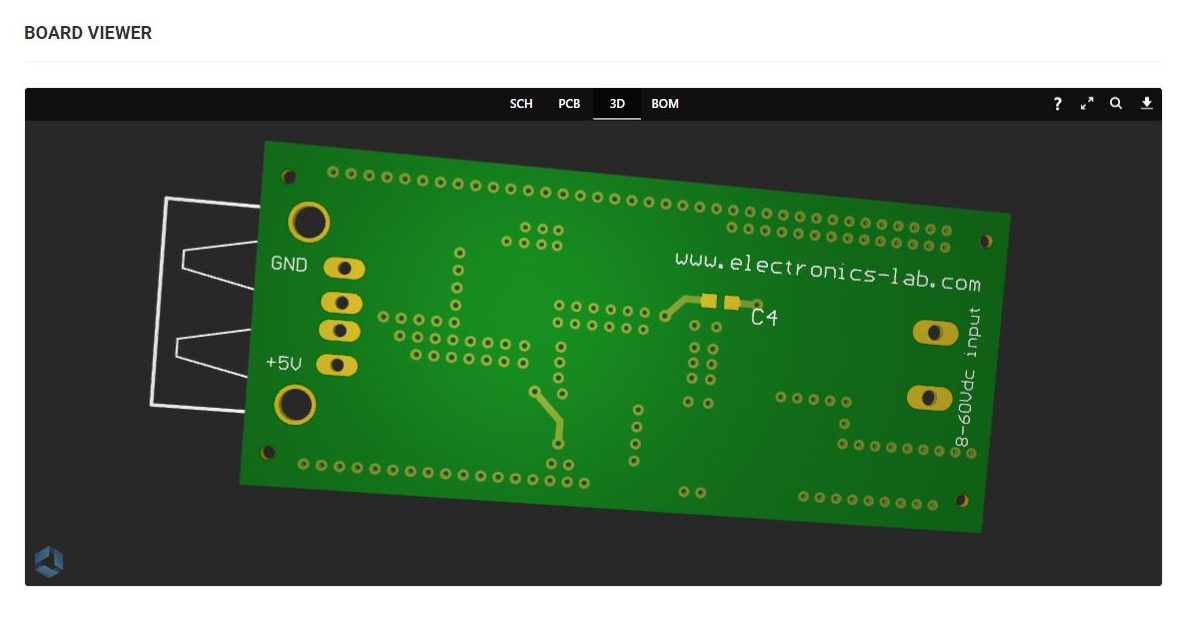

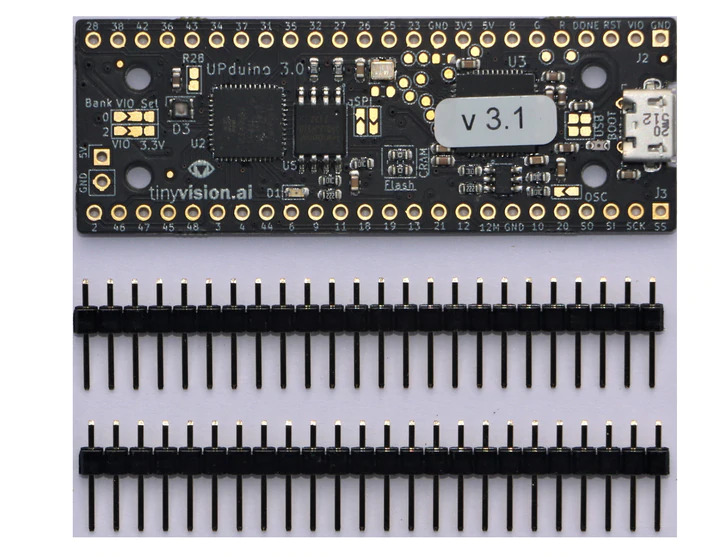

After detecting the connectors ripping off from the board when interfacing, the quality of the USB footprint has grown. Speaking of the USB, please note that the package does not include a USB cable, in order to optimize worldwide shipping. The dimensions of 2.2 cm x 6.2cm x 0.5cm make it a compact and efficient FPGA board. UPduino v3.1 also offers an Open source schematic and layout using KiCAD to make programming easier. The package includes UPduino v3.1 and two 24-pin 0.1″ headers, the user can solder them as per the convenience. The Company tests and programs the UPduino v3.1 with a blinking LED image, before shipping it. The only motive of this test is to keep a track of quality control and ensure the working of the product.

With UPduino v3.1 you can introduce yourself to programming FPGAs since its low cost and the assistance provided by the open-source toolchain. This open-source toolchain is made publicly available enabling the users to experiment and learn about hardware programming. This UPduino v3.1 is available for sale at $25, making it a true cost-efficient FPGA. For more details on the new UPduino v3.1, visit tinyVision.ai