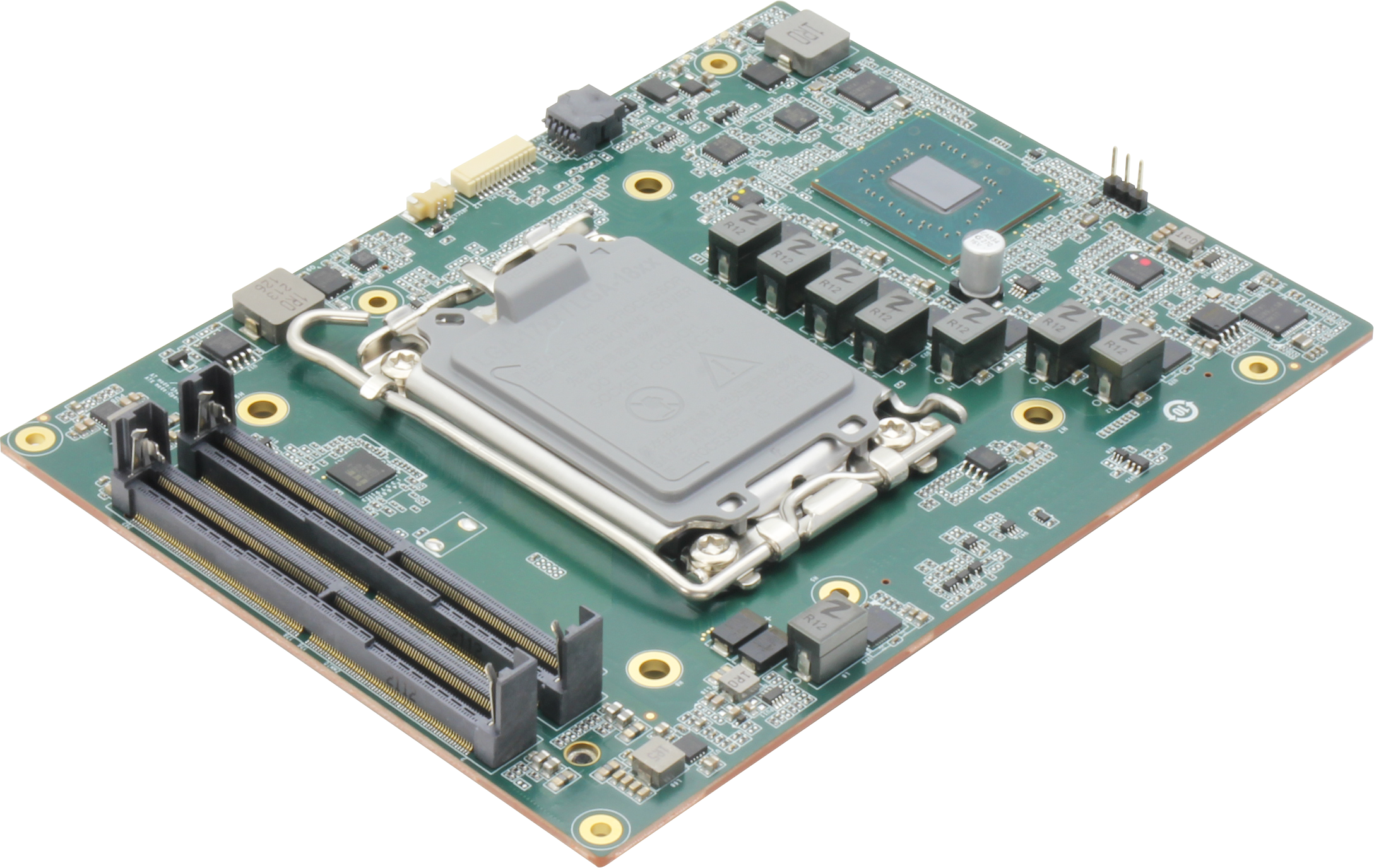

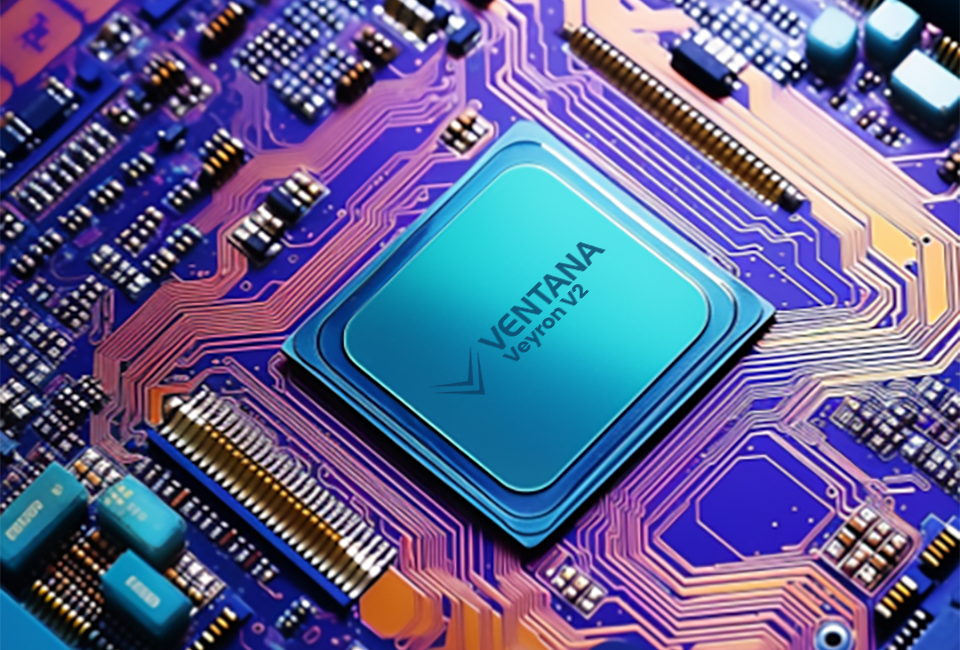

Veyron V2 RISC-V platform Specifications

- CPU Architecture: High-performance RISC-V cores

- Pipeline: Fifteen-wide out-of-order pipeline

- Clock Speed: 3.6GHz

- Process Technology: 4nm

- Core Configuration:

- Up to 32 cores per cluster

- Scalability up to 192 cores across multiple clusters

- Cache: 128MB shared L3 cache per cluster

- Vector Unit: 512-bit vector unit optimized for AI and data-intensive operations

- AI Acceleration: Ventana AI matrix extensions for AI and machine learning tasks

- Memory and Storage:

- Server-class IOMMU support

- Advanced Interrupt Architecture system IP

- Reliability and Security Features:

- Comprehensive RAS (Reliability, Availability, and Serviceability) features

- Side channel attack mitigations for enhanced security

The Veyron V2 platform features Ventana AI matrix extensions for accelerating AI and machine learning workloads. It includes enterprise-level capabilities like server-class IOMMU and Advanced Interrupt Architecture for secure, robust operations, along with RAS features to ensure high system uptime. Security is enhanced through built-in protections against side-channel attacks.

Ventana will present the Veyron V2 RISC-V platform at the RISC-V Summit in Santa Clara on October 22-23. More details are in the official press release.

Subscribe

Login

0 Comments